Sumber :https://onlinelearning.uhamka.ac.id

Senin, 04 Juli 2022

Selasa, 14 Juni 2022

Senin, 06 Juni 2022

Tugas 11 (Ahmad Firdaus Zakaria)Counter

COUNTER

•Counter (pencacah) merupakan register

yang mampu menghitung jumlah pulsa

detak yang masuk melalui masukan

detakannya.

•Pencacah terdiri dari flip-flop yang

diserikan dimana keadaan arus

keluaranya ditahan sampai ada clock .

PEMBAGIAN COUNTER

• Pencacah dapat dibagi menjadi dua tipe, yaitu :

Synchronous dan Asynchonous, dimana keduanya dibedakan dengan bagaimana cara diclock.

• Pencacah Asynchonous didisain dengan menggunakanf lip-flop pada keadaan toggle.

• Flip-flop JK dapat dibuat dalam keadaan toggle dengan menghubungkan kedua input J dan K pada logika 1(high).

• Sedangkan untuk flip-flop tipe D, dapat dibuat dalam keadaan toggle dengan menghubungkan keluaran Q’kembali ke input.

PENCACAH DAPAT DIBEDAKAN MENJADI 2 YAKNI :

1. COUNTER ASYNCHRONOUS (TAK SINKRON)

• Pencacah asynchonous bekerja dengan mengkaskade seri flip-flop dalam keadaan toggle secara bersamaan. Keluaran tiap-tiap flip-flop digunakan sebagai clock untuk flip-flop berikutnya secara berurutan. Hal ini menyebabkan flip-flop berubah secara asynchonous, seperti gelombang.Pencacah asynchonous lebih dikenal sebagai pencacah ripple.

RIPPLE COUNTER

• Gambar di atas memperlihatkan sebuah ripple counter yang dibangun dengan flip-flop JK. Karena masukan J dan K terpasang pada tingkat tegangan High / Logika 1, maka setiap flip-flop akan mengalami toggle ketika masukan detak menerima tepi negatif pulsa.

CARA KERJA RIPPLE COUNTER

• Jika CLk rendah, semua flip-flop akan direset dan menghasilkan kata digital Q3Q2Q1Q0 = 0000. Jika CLK kembali pada logika tinggi, pencacah telah siap melaksanakan operasi. Karena flip-flop paling kanan menerima pulsa detak secara langsung, maka Q0 akan mengalami toggle sekali setiap tepi negatif pulsa detak.

LAJUTANNYA…

• Jika Q0 berubah dari 1 menjadi 0, maka flip-flop Q1 akan menerima sebuah tepi negatif pulsa dan menimbulkan toggle pada keluaran Q1. Demikian selanjutnya jika sebuah flip-flop mengalami reset menjadi nol, maka akan menimbulkan toggle pada flip-flop berikutnya.

CONTROLLED RIPPLE COUNTER

• Sinyal Count untuk mengendalikan pencacah tidak terbergantung pada clock

CARA KERJA CONTROLLED RIPPLE

COUNTER

• Jika COUNT rendah, masukan J dan K akan menjadi rendah. Ini menyebabkan semua flip-flop tertahan dalam keadaan sebelumnya meskipun pulsa-pulsa detak terus memasuki pencacah.

• Bila COUNT tinggi, masukan J dan K ikut menjadi tinggi. Dalam hal ini pencacah akan bekerja sebagaimana telah dibahas sebelumnya, yakni setiap tepi negatif dari pulsa detak akan menambah 1 hitungan pada pencacah

2. COUNTER SYNCHRONOUS (SINKRON)

• Pada pencacah ripple, waktu tunda propagasi total adalah ntd. Ini menyebabkan pencacah ripple terlalu lambat untuk beberapa pemakaian tertentu. Guna mengatasi masalah tersebut, dapat menggunakan sebuah synchronous counter (pencacah sinkron).

• CLR yang rendah akan mereset pencacah menjadi Q = 0000. Ketika sinyal CLR kembali pada keadaan tinggi, pencacah siap beroperasi.

• Tepi positif dari pulsa detak yang pertama akan mengisi Q0 untuk menghasilkan Q = 0001.

• Pada saat tibanya tepi positif yang kedua, Q1 dan Q0 secara serempak mengalami toggle dan kata keluaran menjadi Q = 0010.

• Tepi positif ketiga menaikkan cacahan menjadi Q = 0011, dst. Keuntungan dari pencacah sinkron terletak pada kecepatannya.

• Pencacah ini hanya membutuhkan satu kali waktu tunda propagasi dalam menghasilkan cacahan biner yang tepat sesudah tibanya tepi sinyal detak.

• Pada pencacah sinkron terkendali, sinyal COUNT yang rendah membuat semua flip-flop menjadi tidak aktif. Bila COUNT dijadikan tinggi, rangkaian akan berfungsi sebagai pencacah sinkron. Artinya, setiap tepi positif dari detak akan menaikkan satu angka cacahan.

• Sebuah pencacah lingkar (putar) tidak mencacah dengan bilangan biner tapi bekerja dengan kata-kata yang hanya memiliki satu bit tinggi. Pencacah ini berguna untuk mengendalikan suatu deretan operasi, karena kita dapat mengaktifkan pada setiap saat hanya satu di antara beberapa piranti yang ada.

CARA KERJA RING COUNTER

• Jika CLR rendah dan kemudian menjadi tinggi lagi, maka kata keluaran pertama adalah Q = 0001.

• Tepi pulsa detak yang pertama menggeser bit paling kiri (MSB) ke dalam posisi paling kanan (LSB). Bit-bit yang lain bergeser ke kiri satu posisi sehingga keluaran menjadi Q = 0010.

• Tepi positif yang kedua menyebabkan operasi pemutaran ke kiri berikutnya, sehingga keluaran menjadi Q = 0100.

• Demikian seterusnya hingga tepi positif ke empat memulai siklus yang sama, karena pemutaran ke kiri menghasilkan 0001.

Sumber :

https://onlinelearning.uhamka.ac.id

Selasa, 31 Mei 2022

Tugas 10 Registrasi (Ahmad Firdaus Zakaria)

REGISTER

Register adalah kumpulan elemen-elemen memori yang bekerja bersama sebagai satu unit. Register dapat dibentuk dari rangkaian logika sekuensial yang dibentuk dari flip-flop. Register merupakan sebagian memori dari mikroprosessor yang dapat diakses dengan kecepatan yang sangat tinggi. Dalam melakukan pekerjaannya mikroprosessor selalu menggunakan registerregister sebagai perantaranya sehingga register dapat diibaratkan sebagai kaki dan tangannya dari mikroprosessor.

Dengan kata lain, Register adalah sekumpulan sel biner yang dipakai untuk menyimpan informasi yang disajikan dalam kode-kode biner. Penulisan (pemuatan) informasi itu tidak lain daripada penyetelan keadaan kumpulan flip-flop dalam register itu secara serentak sebagai satu kesatuan. Setiap flip-flop dalam register membentuk satu sel dan dapat menyimpan 1 angka biner (binary digit, bit). Satu register yang tersusun atas n sel dapat menyimpan n bit data yang dapat menyatakan salah satu dari 2n macam kode yang dapat dibentuk dari n bit tersebut, yang untuk data desimal dapat berharga dari 0 sampai dengan 2n-1. Register 8 bit, misalnya, dapat menyimpan salah satu dari 256 macam kode atau harga desimal 0 sampai dengan 255. Register dapat menyimpan informasi dalam kode biner dan menampilkannya kembali dan dikatakan dapat melakukan operasi baca dan tulis.

· Macam Macam Register

Berdasarkan fungsinya , register yaitu ada register buffer dan register shift

1. Register Buffer

Gambar 1 Rangkaian buffer 4 D - FF yang tersambung dalam sebuah rangkaian serial in, serial out shift register.

Register buffer berfungsi untuk menyimpan kata digital. Setiap datang pulsa clock, data dari input D dari masing - masing FF akan di transfer kepada Q output. Pada awalnya, isi dari register diset 0 dengan mengirimkan clock pada clear. Jika 1 merupakan input dari FF yang pertama, maka pada pulsa berikutnya 1 akan di trasnfer ke output FF1 dan sekaligus menjadi input FF2.

a) Register Buffer Tekendali

Register Buffer Terkendali adalah register buffer yang ditambah dengan beberapa gerbang logika dasar AND, OR, dan NOT. Gambar rangkaian menunjukkan sebuah Register buffer terkendali dengan CLR aktif tinggi. Apabila CLR = 1, maka akan terjadi reset pada flip-flop dan data yang tersimpan (Q) menjadi 0000. dan ketika CLR = 0, register siap beroperasi kembali. Sinyal kendali LOAD adalah input kendali yang menentukan operasi rangkaian.Ketika LOAD = 0, semua input data tidak diizinkan masuk, artinya flip-flop mengisolasi input data atau menahan semua data yang ada di dalamnya. Dengan kata lain, register tidak berubah selama LOAD = 0. Ketika LOAD = 1, semua input data akan diterima oleh register. Ketika LOAD kembali = 0, maka input data yang diterima register tadi akan tersimpan dengan aman tanpa gangguan perubahan input.

b) Register Buffer

Adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flipflop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flip-flop ke flip-flop yang lain, kekiri atau kekanan atas perintah denyut lonceng (Clock). Register dapat disusun secara langsung dengan flip-flop. Sebuah flip-flop (FF) dapat menyimpan (store) atau mengingat (memory) atau mencatat (register) data 1 bit.Pada dasarnya, kita dapat membuat register geser (shift register) dengan menggunakan berbagai macam flip-flop, seperti flip-flop RS, JK, D, dan T. Yang penting,rangkaian ini bersifat sinkronus sekuensial, yang berarti bahwa kondisi outputnya ditentukan oleh input, output sekarang (current output) dan setiap output berubah pada waktu yang bersamaan (konotasi dari sinkronus) untuk men-jamin integritas data.Operasi pergeseran data oleh register membuktikan bahwa suatu data biner dapat berpindah tempat, dari satu tempat menuju tempat yang lainnya (flip-flop yang lainnya). Perpindahan terjadi berdasarkan waktu. Register Geser atau Shift Register dapat memindahkan bit-bit yang tersimpan ke kiri atau ke kanan.Pergeseran bit ini penting dalam operasi aritmatika dan operasi logika yang dipakai dalam mikroprosesor (komputer).Dasar dari register geser adalah menggeser data yang disimpannya. Sebagai contoh, sebuah register geser 4-bit akan menggeser data biner yang saling berurutan sebanyak 4 posisi. Proses bergesernya data yang masuk ke dalam register terjadi sejalan dengan sinyal pendetak. Cepat-lambatnya pewaktuan dalam pergeseran dientukan oleh sinyal pendetak yang digunakan. Setiap kali sinyal pendetak berdenyut, maka data yang tersimpan akan bergeser satu posisi. Jika pulsa pendetak berdenyut sekali lagi, maka data yang tersimpan akan bergeser satu posisi lagi. Begitulah dan seterusnya.

Contoh kasus register geser dalam pekerjaan sehari-hari yaitu terdapat pada kalkulator. Bila kita memasukan masing-masing digit pada papan tombol, angka pada peraga akan bergeser ke kiri. Dengan kata lain, untuk memasukkan angka 268 kita harus mengerjakan hal sebagai berikut.

Pertama, kita akan menekan dan melepaskan 2 pada papan tombol, maka 2 muncul pada peraga pada posisi palng kanan. Selanjutnya, kita menekan dan melepaskan 6 pada papan tombol yang menyebabkan 2 bergeser satu posisi ke kiri, yang memungkinkan 6 muncul pada posisi paling kanan, 26 muncul pada peraga. Akhirnya, kita menekan dan melepaskan 8 pada papan tombol, 268 muncul pada peraga.

2. Register Shift

Shift Register merupakan jenis rangkaian logika sekuensial yang dapat digunakan untuk menyimpan data dan juga dapat mentransfer data tersebut. Rangkaian logika sekuensial dari Shift Register akan mengambil data dari saluran input dan kemudian data tersebut akan dipindahkan atau digeser ke bagian output dalam setiap kali siklus clock.Shift Register pada dasarnya merupakan suatu rangkaian beberapa Latch yang disusun membentuk untaian seri sehingga output dari satu Latch akan menjadi input dari Latch berikutnya. Data dapat masuk secara seri yaitu satu per satu baik dari kiri ataupun dari kanan, dan juga dapat masuk secara bersamaan pada rangkaian paralel.

Jumlah Latch yang dibubtuhkan untuk membuat sebuah Shift Register biasanya ditentukan oleh jumlah bit yang akan disimpan. Secara umum, sebuah Shift Register terdiri dari 8 bit ( 1 byte) yang tersusun dari delapan Latch. Semua clock pada setiap Latch dihubungkan menjadi satu (common clock) sehingga perangkat akan sinkron pada saat pengoperasian.Shift Register digunakan untuk menyimpan dan memindahkan data seperti dua buah bilangan biner sebelum ditambahkan bersamaan yang biasa digunakan pada kalkulator atau komputer. Selain itu, Shift Register juga dapat digunakan untuk mengubah data dari seri ke paralel atau dari paralel ke seri.Shift Register secara umum dilengkapi dengan sebuah Clear atau Reset sehingga rangkaian dapat di Set atau Reset sesuai keinginan. Menurut pergerakan data yang dijalankan, Shift Register dapat dibagi menjadi empat kelompok yaitu:

1. Serial Input to Paralel Output (SIPO). Data yang masuk ke Shift Register secara seri, satu bit data untuk setiap siklus Clock. Sedangkan data yang keluar dalam bentuk paralel.

2. Serial Input to Serial Output (SISO). Data yang masuk ke Shift Register secara seri dan keluar juga dalam bentuk seri. Data masuk dan keluar dari Shift Register dikontrol dari Clock.

3. Paralel Input to Serial Output (PISO). Data yang masuk ke Shift Register dalam bentuk paralel secara bersamaan dalam siklus satu Clock. Output berbentuk seri dengan keluaran satu bit untuk setiap Clock.

4. Paralel Input to Paralel Output (PIPO). Data yang masuk ke Shift Register dalam bentuk paralel secara bersamaan dalam satu siklus Clock. Output juga akan keluar secara bersamaan untuk siklus Clock selanjutnya.Shift Register yang digunakan untuk memindahkan atau menggeser data umumnya menggunakan jenis SIPO dan PISO. Sedangkan jenis SISO dan PIPO biasa digunakan untuk menunda pengeluaran data atau berfungsi sebagai delay

Selasa, 24 Mei 2022

Tugas 9 (Ahmad Firdaus Zakaria) Latches, FF, dan Timer

- Latches

Latches dibagi menjadi 3, yaitu : S-R (Set-Reset) Latch , Gated S-R Latch , Gated D Latch

SR-LATCH

- Ujilah SR Berikut ini Jika S=0 dan R=0, Maka berapakah Qn dan Ǭn Nya..?

3. Ujilah SR Berikut ini Jika S=1 dan R=1, Maka berapakah Qn dan Ǭn Nya..?

4.Ujilah SR Berikut ini Jika S=1 dan R=0, Maka berapakah Qn dan Ǭn Nya..?

Sekali lagi, sirkuit multivibrator ini tersedia sebagai perangkat semikonduktor yang dikemas sebelumnya, dan dilambangkan sebagai berikut:

S-R Gated Latch Symbol

SR gated latch symbol

Juga umum untuk melihat input aktifkan yang ditunjuk oleh huruf "EN" bukan hanya "E."

GATED D LATCH

Karena input aktifkan pada gerendel SR yang terjaga keamanannya menyediakan cara untuk mengunci output Q dan bukan-Q tanpa memperhatikan status S atau R, kita dapat menghilangkan salah satu input tersebut untuk membuat rangkaian gerendel multivibrator tanpa input "ilegal" negara bagian.

Sirkuit seperti itu disebut kait D, dan logika internalnya terlihat seperti ini:

SR latch adalah rangkaian berurut yang dapat dibuat dari rangkaian gerbang NOR atau gerbang NAND terkopel, SR latch memiliki dua input yaitu S berarti set dan R berarti reset.Dalam pengujian Set dan Reset (SR) Latch, hasil pengujian tidak boleh melawan dari tabel kebenaran. Ketika memulai pengujian dari R atau S tidak menjadi masalah.SR latch adalah rangkaian berurut yang dapat dibuat dari rangkaian gerbang NOR atau gerbang NAND terkopel, SR latch memiliki dua input yaitu S berarti set dan R berarti reset.Dalam pengujian Set dan Reset (SR) Latch, hasil pengujian tidak boleh melawan dari tabel kebenaran. Ketika memulai pengujian dari R atau S tidak menjadi masalah.

Syarat SR LATCH

a. Pada pengujian menggunakan Gerbang NAND jika S=1 dan R=0 maka proses di lakukan dari R ke S.

b. Jika menggunakan gerbang NOR Ketika S=0 dan R=1 maka proses di lakukan dari R ke S.

c. hasil tidak boleh melawan tabel kebenaran

Contoh kasus SR LATCH – Menggunakan Gerbang NAND

2. Ujilah SR Berikut ini Jika S=0 dan R=1, Maka berapakah Qn dan Ǭn Nya..?

Note no.4 : Ketika S=1 dan R=0 maka proses di lakukan dari R ke S. yang jelas hasil tidak boleh melawan tabel kebenaran

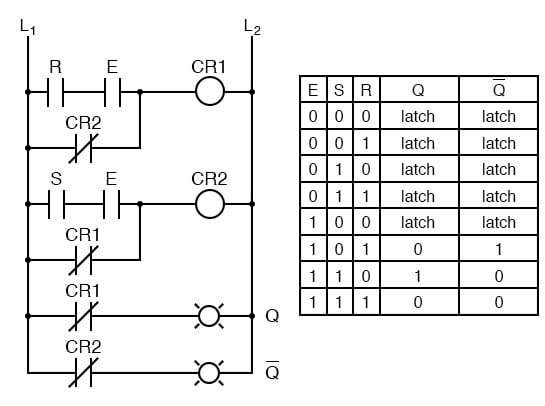

GATED S-R LATCH

Terkadang berguna dalam rangkaian logika untuk memiliki multivibrator yang mengubah status hanya ketika kondisi tertentu terpenuhi, terlepas dari status input S dan R-nya.

Input bersyarat disebut aktifkan, dan dilambangkan dengan huruf E. Pelajari contoh berikut untuk melihat cara kerjanya:

Gated SR- Latch Truth Table

Ketika E=0, output dari dua gerbang AND dipaksa ke 0, terlepas dari status S atau R. Akibatnya, rangkaian berperilaku seolah-olah S dan R keduanya 0, mengunci output Q dan bukan-Q di negara terakhir mereka.

Hanya ketika input aktifkan diaktifkan (1) kait akan merespons input S dan R. Perhatikan fungsi identik dalam logika tangga:

Gated S-R Latch Ladder Logic

Aplikasi praktis dari ini mungkin sirkuit kontrol motor yang sama (dengan dua sakelar tombol tekan yang biasanya terbuka untuk start dan stop), kecuali dengan penambahan input penguncian master (E) yang menonaktifkan kedua tombol tekan agar tidak memiliki kendali atas motor. saat rendah (0).

Perhatikan bahwa input R telah diganti dengan komplemen (inversi) dari input S lama, dan input S telah diubah namanya menjadi D. Seperti halnya gerendel S-R dengan gerbang, kait D tidak akan merespons input sinyal jika diaktifkan inputnya adalah 0—itu tetap terkunci di status terakhirnya. Namun, ketika input aktifkan adalah 1, output Q mengikuti input D.

Karena input R dari sirkuit S-R telah dihilangkan, kait ini tidak memiliki status "tidak valid" atau "ilegal". Q dan bukan-Q selalu berlawanan satu sama lain.

TimerMonostable (one-shot) operationMultivibrator monostabil, juga disebut satu tembakan atau monoflop, adalah rangkaian elektronik logika sekuensial yang menghasilkan pulsa keluaran. Saat dipicu, pulsa dengan durasi yang telah ditentukan sebelumnya diproduksi. Sirkuit kemudian kembali ke keadaan stabil dan tidak menghasilkan output lagi sampai dipicu lagi.

Astable operationKonfigurasi astabil menghasilkan aliran pulsa yang berkelanjutan dengan panjang dan frekuensi tetap. Disebut astabil karena tidak memiliki keadaan stabil, terus menerus bolak-balik.

Ini sangat mirip dengan sirkuit monostabil dengan dua perbedaan yang tampaknya kecil:

Ada resistor kedua (R2) antara debit dan kapasitor / ambang batas.Pemicu terhubung ke ambang, bukan menjadi input eksternal.Karena perbedaan ini, operasinya sangat berbeda.

Seperti sebelumnya, C1 mengisi daya, tetapi kali ini melalui kombinasi R1 dan R2. Karena input pemicu adalah tegangan pada C1, 555 terpicu ketika C1 dilepaskan ke 1/3Vcc, di mana flipflop akan disetel dan C1 mulai mengisi daya lagi. Ini berarti bahwa C1 tidak pernah melepaskan ke 0v sehingga ketika mengisi tidak tidak mengisi dari 0v, itu berubah dari 1/3Vcc. Efek praktisnya adalah waktu pengisian tidak penuh (R1+R2)C. Sebaliknya dibutuhkan 0,693(R1+R2)C1 detik. Mengapa 0,693? Matematika.

Ketika pin pelepasan ditanahkan sebagai respons terhadap tegangan kapasitor / ambang mencapai 2/3Vcc, C1 melepaskan melalui R2. Ini membutuhkan waktu yang ditentukan oleh R2 dan C1. Sekali lagi C1 mengeluarkan dari 2/3Vcc ke 1/3Vcc sehingga waktunya menjadi 0,693(R2C1).

Senin, 09 Mei 2022

Senin, 25 April 2022

TUGAS 8 (Ahmad Firdaus Zakaria) Fungsi Kombinasi Logika

FUNGSI KOMBINASI LOGIKA

- Bedakan antara half-adder dan full-adder

- Gunakan decoder bcd-to-7-segment dalam sistem tampilan

- Menerapkan Multiplekser dalam pemilihan data

- Gunakan Decoder sebagai multiplekser

0 + 0 = 0 Nol ditambah nol sama dengan nol

0 + 1 = 1 Nol ditambah satu sama dengan satu

1 + 0 = 1 Satu ditambah nol sama dengan satu

1 + 1 = 1 Satu ditambah satu sama dengan nol dengan membawa satu

ADDER DASAR

Adder penting dalam komputer dan juga dalam jenis sistem digital lainnya di mana data numerik diproses Setengah adder menerima dua digit biner pada inputnya dan menghasilkan dua digit biner pada outputnya, jumlah bit dan carry bit.

Full-adder harus menambahkan dua bit input dan input carry. Dari half-adder, jumlah bit input A dan B adalah eksklusif-OR dari kedua variabel tersebut. Agar input carry (Cin) ditambahkan ke bit input, itu harus eksklusif-ORed, dan terakhir menghasilkan persamaan untuk jumlah output dari full-adder

Ini berarti bahwa untuk menerapkan fungsi jumlah full-adder, dua gerbang exclusive-OR 2-input dapat digunakan . Yang pertama harus menghasilkan istilah AB dan yang kedua memiliki sebagai input output dari gerbang XOR pertama dan input membawa. Output carry adalah 1 ketika kedua input ke gerbang XOR pertama adalah 1s atau ketika kedua input ke gerbang XOR kedua adalah 1s. Output carry dari full-adder oleh karena itu diproduksi oleh input A ANDed dengan B dan AB ANDed dengan Cin.

Selasa, 19 April 2022

TUGAS 7 (AHMAD FIRDAUS ZAKARIA) BOOLEAN & KARNAUGH MAP

Karnaugh Map

Kmap memiliki beberapa kelebihan, diantaranya adalah lebih sederhana dalam proses penyederhanaannya untuk memperoleh jumlah literal yang lebih sedikit. Apabila ada fungsi n variabel, dibutuhkan 2 n baris table kebenaran, dan pada Kmap dibutuhkan 2n kotak persegi. Nilai dari table kebenaran tersebut ditulis kembali di kota k persegi pada posisi yang mewakli posisinya di table kebenaran. Langkah - langkah menyajikan fungsi ke dalam Kmap adalah :

- Buat diagram matriks sebanyak 2 n kotak persegi, dimana n adalah jumlah variable fungsi.

- Setiap kotak- kotak persegi tersebut diisi sesuai dengan nilai yang diberikan dari fungsi atau nilai dari table kebenaran pada letak yang tepat.

Penyajian KMap 2 Variabel

Pada penyajian Kmap 2- variabel dibutuhkan 4 (2n) kotak persegi untuk Kmap. Cara mengisi masing - masing kotak persegi pada Kmap ditunjukkan pada gambar ... Terdapat berbagai macam cara dalam menyusun matriks Kmap dan kita boleh memilih, dengan syarat tetap konsisten pada posisi dimana minterm berada.

Penyajian KMap 3 Variabel

Pada penyajian Kmap 3 - variabel dibutuhkan 8 2 3) kotak persegi untuk Kmap. Cara mengisi masing - masing kotak persegi pada Kmap ditunjukkan pada gambar dibawah

Pada susunan matriks Kmap 3 - varaibel ke atas, terdapat urutan matriks yang harus diperhatikan. Pada matriks Kmap, dari setelah m 1 (x’y’z) urutan selanjutnya adalah m 3 (x’.y.z), bukan m 2 (x’yz’). Begitu pula m 5 (xy’z) urutan selanjutnya adalah m 7 (xyz), bukan m 6 (xyz’). Hal ini terjadi, disebabkan pada aturan pengurutan Kmap, kotak yang bersebelahan haruslah hanya memiliki satu perubahan bit variable, dari 0 ke 1 atau dari 1 ke 0. Apabila urutan setelah m (x’y’z) adalah m 2 (x’yz’), maka terdapat dua bit variable yang berubah yaitu y dan z. Bit variable y berubah dari y’ menjadi y dan bit variable z berubah dari z menjadi z’. Begitu pula yang terjadi pada m 5 (xy’z), apabila urutan setelah m 5 (xy’z) adalah m 6 (xyz’), maka terdapat dua bit variable yang berubah yaitu y dan z. Bit variable y berubah dari y’ menjadi y dan bit variable z berubah dari z menjadi z’.

KMap 4 Variabel

SOAL :

1. Peta karnaugh (atau K-Map) diperkenalkan oleh?

A. Maurice Karnaugh

B. Thomas edison

C. Alexander G

D. Aris Totles

2. Apa yang di maksud dengan Peta Karnaugh ?

A. Menyederhanakan sebuah fungsi persamaan saja

B. Menyederhanakan sebuah fungsi persamaan logika

C. Menyederhanakan sebuah fungsi persamaan bilangan

D. Memudahkan sebuah fungsi persamaan logika

SUMBER : https://onlinelearning.uhamka.ac.id/

Selasa, 12 April 2022

Senin, 04 April 2022

Tugas 5 (Ahmad Firdaus Zakaria) Aljabar Boolean

Aljabar Boolean

OPERASI ALJABAR BOOLEAN DUA VARIABEL DAN TIGA VARIABEL

- Hukum Komutatif

- Hukum Asosiatif

- Hukum Distributif

Sumber : https://onlinelearning.uhamka.ac.id

Senin, 28 Maret 2022

Tugas 4 (Ahmad Firdaus Zakaria) Gerbang Logika

GERBANG LOGIKA DAN ALJABAR BOOLEAN

- Aljabar Boolean adalah alat yang penting dalam menggambarkan, menganalisa, merancang, dan mengimplementasikan rangkaian digital.

KONSTANTA BOOLEAN DAN VARIABEL

- Aljabar boolean di bawah ini hanya mempunyai dua nilai : 0 dan 1.

- Logika 0 dapat dikatakan : false, off, low, no, dan saklar terbuka.

- Logika 1 dapat dikatakan : true, on, high, yes, dan saklar tertutup.

- Tiga operasi logika dasar : OR, AND, dan NOT.

TABEL KEBENARAN

- Sebuah tabel kebenaran menggambarkan hubungan antara input dan output sebuah rangkaian antara input dan output sebuah rangkaian logika.

- Jumlah-jumlah entri sesuai dengan jumlah input. Misalnya input 2 meja akan memiliki 2, 2 = 4 entri. 3 masukan meja akan memiliki 2, 3 = 8 entri.

OPERASI OR DENGAN GERBANG OR

- Ekspresi Boolean untuk operasi OR adalah X = A+B. Ini dibaca sebagai " sama dengan A atau B." X = 1 jika A = 1 atau B = 1.

OR OPERATION WITH OR GATES

- Operasi Or mirip dengan penjumlahan tetapi ketika A = 1 dan B = 1, operasi OR menghasilkan 1 1+1= 1.

- Ada banyak contoh aplikasi di mana fungsi output diinginkan ketika salah satu dari beberapa input diaktifkan.

AND OPERATIONS WITH AND GATES

- Ekspresi Boolean untuk operasi AND adalah X = A • B Ini dibaca sebagai "x sama dengan A dan B." x = 1 ketika A = 1 dan B = 1.

- Tabel kebenaran dan simbol rangkaian untuk gerbang AND dua masukan adalah ditampilkan.

OPERATION WITH AND GATES

- Operasi AND mirip dengan perkalian.

- Dalam ekspresi Boolean X = A • B • C X = 1 hanya jika A = 1, B = 1, dan C = 1.

NOT OPERATION

- Ekspresi Boolean untuk NOT operasi adalah X = A

- Ini dibaca sebagai: x sama dengan NOT A, atau x sama dengan invers dari A, atau x sama dengan komplemen dari A.

- Tabel kebenaran, simbol, dan bentuk gelombang sampel untuk sirkuit NOT.

DESCRIBING LOGIC CIRCUITS ALGEBRAICALLY

- Tiga operasi Boolean dasar (OR, AND, NOT) dapat menggambarkan rangkaian logika apa pun.

- Jika ekspresi mengandung AND dan OR gerbang operasi AND akan dilakukan pertama, kecuali ada tanda kurung di dalam ekspresi.

EVALUATING LOGIC CIRCUIT OUTPUTS

- Aturan untuk mengevaluasi ekspresi Boolean:

- Lakukan semua inversi istilah tunggal

- Lakukan semua operasi dalam kurung.

- Lakukan operasi AND sebelum operasi OR

- Lakukan operasi AND sebelum operasi OR

- kecuali tanda kurung menunjukkan sebaliknya.

- Jika ekspresi memiliki bilah di atasnya, lakukan operasi di dalam ekspresi dan kemudian invert hasil.

- Evaluasi ekspresi Boolean dengan mensubstitusi nilai-nilai dan melakukan yang ditunjukkan operasi.

- Level logika keluaran dapat ditentukan secara langsung dari diagram sirkuit.

- Output dari setiap gerbang dicatat sampai final keluaran ditemukan.

-dikonversi_20220607_4198614174909093129.png)

-dikonversi_20220607_2409160068323860191.png)

-dikonversi_20220607_5535893832123020554.png)

-dikonversi_20220607_3156932625886599206.png)

.jpeg)